### 1MHz, General Purpose, RRIO CMOS Amplifiers

## **General Description**

The LMV321 (single), LMV358 (dual) and LMV324 (quad) are general purpose, low offset, high frequency response and micro power operational amplifiers. With an excellent bandwidth of 1MHz, a slew rate of  $0.8V/\mu s$ , and a quiescent current of  $80\mu A$  per amplifier at 5V, the LMV321/358/324 family can be designed into a wide range of applications.

The LMV321/358/324 op-amps are designed to provide optimal performance in low voltage and low power systems. The input common-mode voltage range includes ground, and the maximum input offset voltage are 4.5mV. These parts provide rail-to-rail output swing into heavy loads. The LMV321/358/324 family is specified for single or dual power supplies of +1.8V to +5.5V. All models are specified over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

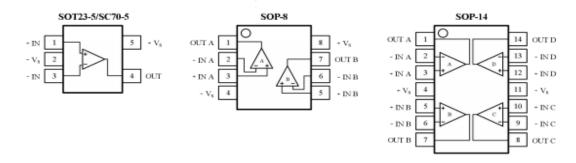

The LMV321 is available in 5-lead SOT-23 and SC70-5 package. The LMV358 is available in 8-lead SOP package. The LMV324 is available in 14-lead SOP package.

#### **Features**

- General Purpose 1MHz Amplifiers, Low Cost

- High Slew Rate: 0.8V/μs

- Low Offset Voltage: 4.5 mV Maximum

- Low Power: 80µA per Amplifier Supply Current

- Settling Time to 0.1% with 2V Step: 4.2 μs

- Unit Gain Stable

- Rail-to-Rail Input and Output

- ➤ Input Voltage Range: -0.1V to +5.1V at 5V Supply

- Operating Power Supply: +1.8V to +5.5V

- Operating Temperature Range:  $-40^{\circ}$ C to  $+125^{\circ}$ C

- ESD Rating: HBM-4kV, CDM-2kV

## **Applications**

- Smoke/Gas/Environment Sensors

- Audio Outputs

- Battery and Power Supply Control

- Portable Equipment and Mobile Devices

- Active Filters

- Sensor Interfaces

www.slkormicro.com 1 Rev.2 -- 21 July 2023

# **Applications**

- Battery-Powered Instrumentation

- Medical Instrumentation

## **Pin Configurations**

Figure 1 Pin Configurations

## **Pin Description**

| Symbol                   | Description                                                                                                                                                                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IN                      | Negative (inverting) input.                                                                                                                                                                                                                                                                                        |

| +IN                      | Positive (noninverting) input.                                                                                                                                                                                                                                                                                     |

| -INA, -INB<br>-INC, -IND | Inverting Input of the Amplifier. The Voltage range can go from $(V_{S^-}-0.1V)$ to $(V_{S^+}+0.1V)$ .                                                                                                                                                                                                             |

| +INA, +INB<br>+INC, +IND | Non-Inverting Input of Amplifier. This pin has the same voltage range as -IN.                                                                                                                                                                                                                                      |

| +V <sub>S</sub>          | Positive Power Supply. The voltage is from 1.8V to 5.5V. Split supplies are possible as long as the voltage between $V_{S^+}$ and $V_{S^-}$ is between 1.8V and 5.5V. A bypass capacitor of $0.1\mu F$ as close to the part as possible should be used between power supply pins or between supply pins and ground |

| -V <sub>S</sub>          | Negative Power Supply. It is normally tied to ground. It can also be tied to a voltage other than ground as long as the voltage between $V_{S^+}$ and $V_{S^-}$ is from 1.8V to 5.5V. If it is not connected to ground, bypass it with a capacitor of $0.1\mu F$ as close to the part as possible.                 |

| OUT                      | Output.                                                                                                                                                                                                                                                                                                            |

| OUTA, OUTB<br>OUTC, OUTD | Amplifier Output                                                                                                                                                                                                                                                                                                   |

www.slkormicro.com 2 Rev.2 -- 21 July 2023

# **Ordering Information**

| Type Number | Package | Number of package |

|-------------|---------|-------------------|

| LMV321 XC5  | SC70-5  | 3000 PCS          |

| LMV321 XT5  | SOT23-5 | 3000 PCS          |

| LMV358 XS8  | SOP-8   | 4000 PCS          |

| LMV324XS14  | SOP-14  | 2500 PCS          |

# Absolute Maximum Ratings (T<sub>A</sub>= 25°C)

| Symbol              | Description                               | Value                            | Units               |

|---------------------|-------------------------------------------|----------------------------------|---------------------|

| $V_{S^+\!,}V_{S^-}$ | Supply Voltage, $V_{S^+}$ to $V_{S^-}$    | 7.0                              | V                   |

| $V_{\text{CM}}$     | Common-Mode Input Voltage                 | $V_{S-}$ – 0.3 to $V_{S+}$ + 0.3 | V                   |

| EGD                 | Electrostatic Discharge Voltage           | HBM ±4000                        | V                   |

| ESD                 |                                           | CDM ±2000                        | V                   |

| $T_{\rm J}$         | Junction Temperature                      | 160                              | °C                  |

| $T_{STG}$           | Storage Temperature Range                 | -65 to +150                      | °C(T <sub>J</sub> ) |

| ${ m T_{JL}}$       | Lead Temperature Range (Soldering 10 sec) | 260                              | °C                  |

#### Notes:

www.slkormicro.com 4 Rev.2 -- 21 July 2023

<sup>1.</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> Provided device does not exceed maximum junction temperature (T<sub>J)</sub> at any time.

## **Electrical Characteristics**

$V_S = 5.0 V$ ,  $T_A = +25 \,^{\circ}\text{C}$ ,  $V_{CM} = V_S/2$ ,  $V_O = V_S/2$ , and  $R_L = 10 \text{k}\Omega$  connected to  $V_S/2$ , unless otherwise noted.

| mV<br>μV/°C<br>pA |  |

|-------------------|--|

| μV/°C             |  |

| μV/°C             |  |

| •                 |  |

| pA                |  |

| pA                |  |

| 100               |  |

| pA                |  |

| V                 |  |

|                   |  |

| ДЪ                |  |

| dB                |  |

|                   |  |

|                   |  |

| dB                |  |

| GΩ                |  |

|                   |  |

| pF                |  |

| _                 |  |

| mV                |  |

| mV                |  |

|                   |  |

| Ω                 |  |

|                   |  |

| mA                |  |

|                   |  |

|                   |  |

| MHz               |  |

| MHz<br>°          |  |

| _                 |  |

## **Electrical Characteristics**

$V_S = 5.0V, \ T_A = +25\,^{\circ}\text{C}, \ V_{CM} = V_S/2, \ V_O = V_S/2, \ \text{and} \ R_L = 10 \text{k}\Omega \ \text{connected to} \ V_S/2, \ \text{unless otherwise noted}.$

| Symbol                  | Parameter                         | Conditions                                  | Min. | Тур.  | Max. | Unit          |  |

|-------------------------|-----------------------------------|---------------------------------------------|------|-------|------|---------------|--|

|                         |                                   | To $0.1\%$ , $G = +1$ , $2V$ step           |      | 4.2   |      |               |  |

| ts                      | Settling time                     | To $0.01\%$ , $G = +1$ , $2V$ step          |      | 5.2   |      | μs            |  |

| tor                     | Overload recovery time            | $V_{IN} * Gain > V_S$                       |      | 2     |      | μs            |  |

| THD+N                   | Total harmonic distortion+Noise   | $f = 1 \text{kHz}, G = +1, V_{O} = 3V_{PP}$ |      | 0.003 |      | %             |  |

| NOISE PEI               | RFORMANCE                         |                                             |      |       |      |               |  |

| $V_n$                   | Input voltage noise               | f = 0.1  to  10  Hz                         |      | 13    |      | $\mu V_{P-P}$ |  |

| en                      | Input voltage noise density       | f = 1kHz                                    |      | 35    |      | nV/√Hz        |  |

| In                      | Input current noise density       | f = 10kHz                                   |      | 6     |      | fA/√Hz        |  |

| POWER SU                | JPPLY                             |                                             |      |       |      |               |  |

| Vs                      | Operating supply voltage          |                                             | 1.8  |       | 5.5  | V             |  |

|                         | Power supply rejection ratio      | $V_S = 2.7V$ to 5.5V,                       |      | 98    |      | 1D            |  |

| PSRR                    | Over temperature                  | $V_{CM} < V_{S^+} - 2V$                     |      | 85    |      | dB            |  |

| т                       | Quiescent current (per amplifier) |                                             |      | 80    | 120  | 4             |  |

| $I_Q$                   | Over temperature                  |                                             |      | 85    | 130  | μΑ            |  |

| THERMAL CHARACTERISTICS |                                   |                                             |      |       |      |               |  |

| $T_A$                   | Operating temperature range       |                                             | -40  |       | +125 | °C            |  |

| $	heta_{ m JA}$         | Package thermal resistance        | SOT23-5                                     |      | 190   |      |               |  |

|                         |                                   | SO-8                                        |      | 125   |      | °C/W          |  |

|                         |                                   | SO-14                                       |      | 115   |      |               |  |

Specifications subject to changes without notice

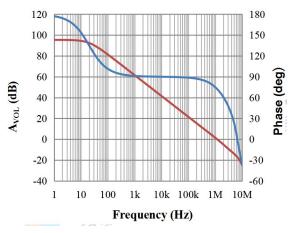

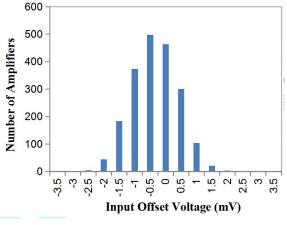

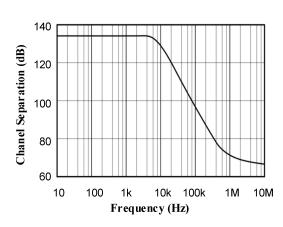

## **Typical Performance Characteristics**

At  $T_A$  = +25 °C,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10k $\Omega$  connected to  $V_S/2$ , unless otherwise noted.

120

100

80

80

40

PSRR

40

20

1 10 100 1k 10k 100k 1M 10M

Frequency (Hz)

Figure 2 Open-loop Gain and Phase as a function of Frequency

Figure 3 Power Supply and Common-mode RejectionRatio as a function of Frequency

Figure 4 Input Offset Voltage Production Distribution

Figure 5 Channel Separation as a function of Frequency

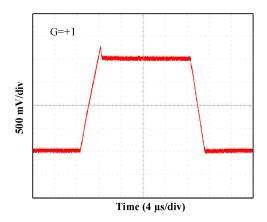

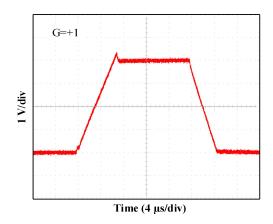

Figure 6 Large-Signal Step Response at 2.7V

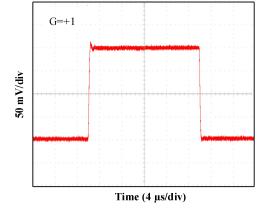

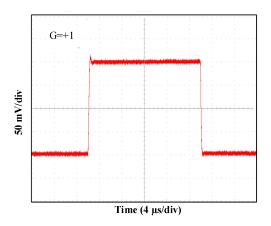

Figure 7 Small-Signal Step Response at 2.7V

www.slkormicro.com 7 Rev.2 -- 21 July 2023

# **Typical Performance Characteristics**

At  $T_A$  = +25 °C,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10k $\Omega$  connected to  $V_S/2$ , unless otherwise noted.

Figure 8 Large-Signal Step Response at 5V

Figure 9 Small-Signal Step Response at 5V

#### 1. LOW INPUT BIAS CURRENT

The LMV321/358/324 family is a CMOS op-amp family and features very low input bias current in pA range. The low input bias current allows the amplifiers to be used in applications with high resistance sources. Care must be taken to minimize PCB Surface Leakage. See below section on "PCB Surface Leakage" for more details.

#### 2. PCB SURFACE LEAKAGE

In applications where low input bias current is critical, Printed Circuit Board (PCB) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low humidity conditions, a typical resistance between nearby traces is  $10^{12}\Omega$ . A 5V difference would cause 5pA of current to flow, which is greater than the LMV321/358/324's input bias current at +25°C ( $\pm$ 1pA, typical). It is recommended to use multi-layer PCB layout and route the op-amp's -IN and +IN signal under the PCB surface.

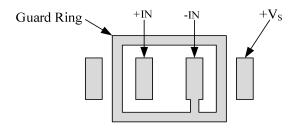

The effective way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 10 for Inverting Gain application.

- 1. For Non-Inverting Gain and Unity-Gain Buffer:

- a) Connect the non-inverting pin (+IN) to the input with a wire that does not touch the PCB surface.

- b) Connect the guard ring to the inverting input pin (-IN). This biases the guard ring to the Common Mode input voltage.

- 2. For Inverting Gain and Trans-impedance Gain Amplifiers (convert current to voltage, such as photo detectors):

- a) Connect the guard ring to the non-inverting input pin (+IN). This biases the guard ring to the same reference voltage as the op-amp (e.g.,  $V_s/2$  or ground).

- b) Connect the inverting pin (-IN) to the input with a wire that does not touch the PCB surface.

Figure 10 Use a guard ring around sensitive pins

www.slkormicro.com 9 Rev.2 -- 21 July 2023

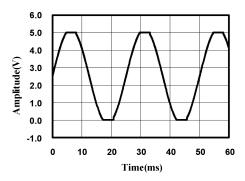

#### 3. GROUND SENSING AND RAIL TO RAIL

The input common-mode voltage range of the LMV321/358/324 series extends 100 mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair. For normal operation, inputs should be limited to this range. The absolute maximum input voltage is 300 mV beyond the supplies. Inputs greater than the input common-mode range but less than the maximum input voltage, while not valid, will not cause any damage to the op-amp. Unlike some other op-amps, if input current is limited, the inputs may go beyond the supplies without phase inversion, as shown in Figure 11. Since the input common-mode range extends from  $(V_{S-}-0.1 \text{V})$  to  $(V_{S+}+0.1 \text{V})$ , the LMV321/358/324 op-amps can easily perform 'true ground' sensing.

Figure 11 No Phase Inversion with Inputs Greater Than the Power-Supply Voltage

A topology of class AB output stage with common-source transistors is used to achieve rail-to-rail output. For light resistive loads (e.g.  $100k\Omega$ ), the output voltage can typically swing to within 5mV from the supply rails. With moderate resistive loads (e.g.  $10k\Omega$ ), the output can typically swing to within 10mV from the supply rails and maintain high open-loop gain.

The maximum output current is a function of total supply voltage. As the supply voltage to the amplifier increases, the output current capability also increases. Attention must be paid to keep the junction temperature of the IC below 150°C when the output is in continuous short-circuit. The output of the amplifier has reverse-biased ESD diodes connected to each supply. The output should not be forced more than 0.5V beyond either supply, otherwise current will flow through these diodes.

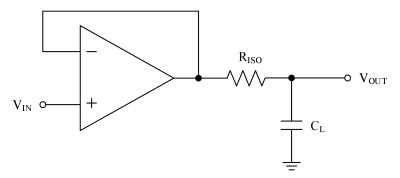

#### 4. CAPACITIVE LOAD AND STABILITY

The LMV321/358/324 can directly drive 1nF in unity-gain without oscillation. The unity-gain follower (buffer) is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers and this results in ringing or even

www.slkormicro.com 10 Rev.2 -- 21 July 2023

oscillation. Applications that require greater capacitive drive capability should use an isolation resistor between the output and the capacitive load like the circuit in Figure 12. The isolation resistor  $R_{\rm ISO}$  and the load capacitor  $C_L$  form a zero to increase stability. The bigger the  $R_{\rm ISO}$  resistor value, the more stable  $V_{\rm OUT}$  will be. Note that this method results in a loss of gain accuracy because  $R_{\rm ISO}$  forms a voltage divider with the  $R_L$ .

Figure 12 Indirectly Driving Heavy Capacitive Load

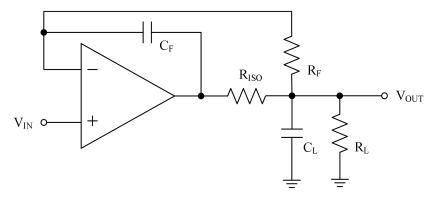

An improvement circuit is shown in Figure 13. It provides DC accuracy as well as AC stability. The  $R_F$  provides the DC accuracy by connecting the inverting signal with the output. The  $C_F$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop.

Figure 13 Indirectly Driving Heavy Capacitive Load with DC Accuracy

For no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier's gain, or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.

#### 5. POWER SUPPLY LAYOUT AND BYPASS

The LMV321/358/324 family operates from either a single  $\pm 1.8V$  to  $\pm 5.5V$  supply or dual  $\pm 0.9V$  to  $\pm 2.75V$  supplies. For single-supply operation, bypass the power supply  $V_S$

www.slkormicro.com 11 Rev.2 -- 21 July 2023

with a ceramic capacitor (i.e.  $0.01\mu F$  to  $0.1\mu F$ ) which should be placed close (within 2mm for good high frequency performance) to the  $V_S$  pin. For dual-supply operation, both the  $V_{S^+}$  and the  $V_{S^-}$  supplies should be bypassed to ground with separate  $0.1\mu F$  ceramic capacitors. A bulk capacitor (i.e.  $2.2\mu F$  or larger tantalum capacitor) within 100mm to provide large, slow currents and better performance. This bulk capacitor can be shared with other analog parts.

Good PC board layout techniques optimize performance by decreasing the amount of stray capacitance at the op-amp's inputs and output. To decrease stray capacitance, minimize trace lengths and widths by placing external components as close to the device as possible. Use surface-mount components whenever possible. For the op-amp, soldering the part to the board directly is strongly recommended. Try to keep the high frequency big current loop area small to minimize the EMI (electromagnetic interfacing).

#### 6. GROUNDING

A ground plane layer is important for the LMV321/358/324 circuit design. The length of the current path speed currents in an inductive ground return will create an unwanted voltage noise. Broad ground plane areas will reduce the parasitic inductance.

#### 7. INPUT-TO-OUTPUT COUPLING

To minimize capacitive coupling, the input and output signal traces should not be parallel. This helps reduce unwanted positive feedback.

## **Typical Application Circuits**

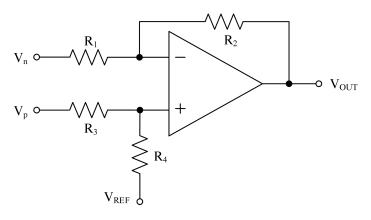

#### 1. DIFFERENTIAL AMPLIFIER

Figure 14 Differential Amplifier

The circuit shown in Figure 14 performs the difference function. If the resistors ratios are equal  $R_4/R_3 = R_2/R_1$ , then:

$$V_{OUT} = (V_p - V_n) \times R_2/R_1 + V_{REF}$$

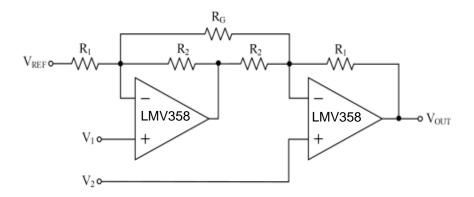

#### 2. INSTRUMENTATION AMPLIFIER

$$V_{OUT} = (V_1 - V_2) \times (1 + R_1/R_2 + 2R_1/R_G) + V_{REF}$$

Figure 15 Instrumentation Amplifier

The LMV321/358/324 family is well suited for conditioning sensor signals in battery-powered applications. Figure 15 shows a two op-amp instrumentation amplifier, using the LMV358 op-amps. The circuit works well for applications requiring rejection of common-mode noise at higher gains. The reference voltage ( $V_{REF}$ ) is supplied by a low-impedance source. In single voltage supply applications, the  $V_{REF}$  is typically  $V_{S}/2$ .

www.slkormicro.com 13 Rev.2 -- 21 July 2023

## **Typical Application Circuits**

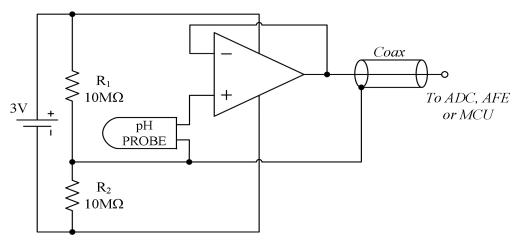

#### 3. BUFFERED CHEMICAL SENSORS

All components contained within the pH probe

Figure 16 Buffered pH Probe

The LMV321/358/324 family has input bias current in the pA range. This is ideal in buffering high impedance chemical sensors, such as pH probes. As an example, the circuit in Figure 16 eliminates expansive low-leakage cables that is required to connect a pH probe (general purpose combination pH probes, e.g Corning 476540) to metering ICs such as ADC, AFE and/or MCU. An LMV321/358/324 op-amp and a lithium battery are housed in the probe assembly. A conventional low-cost coaxial cable can be used to carry the op-amp's output signal to subsequent ICs for pH reading.

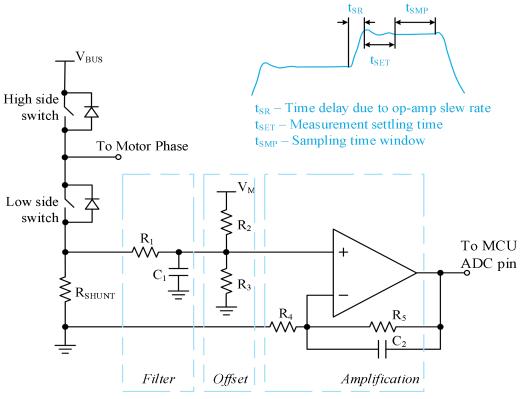

#### 4. SHUNT-BASED CURRENT SENSING AMPLIFIER

The current sensing amplification shown in Figure 8 has a slew rate of  $2\pi fV_{PP}$  for the output of sine wave signal, and has a slew rate of  $2fV_{PP}$  for the output of triangular wave signal. In most of motor control systems, the PWM frequency is at 10kHz to 20kHz, and one cycle time is  $100\mu$ s for a 10kHz of PWM frequency. In current shunt monitoring for a motor phase, the phase current is converted to a phase voltage signal for ADC sampling. This sampling voltage signal must be settled before entering the ADC. As the Figure 19 shown, the total settling time of a current shunt monitor circuit includes: the rising edge delay time ( $t_{SR}$ ) due to the op-amp's slew rate, and the measurement settling time ( $t_{SET}$ ). For a 3-shunt solution in motor phase current sensing, if the smaller duty cycle of the PWM is defined at 45% (In fact, the phase with minimum PWM duty cycle, such as 5%, is not detected current directly, and it can be calculated from the other two phase currents), and the  $t_{SR}$  is required at 20% of a total time window for a phase current monitoring, in case of a 3.3V motor control system(3.3V MCU with 12-bit ADC), the op-amp's slew rate should be more than:

# **Typical Application Circuits**

#### $3.3V/(100\mu s \times 45\% \times 20\%) = 0.37 V/\mu s$

At the same time, the op-amp's bandwidth should be much greater than the PWM frequency, like 10 time at least.

Figure 17 Current Shunt Monitor Circuit

www.slkormicro.com 15 Rev.2 -- 21 July 2023

# **Package Information**

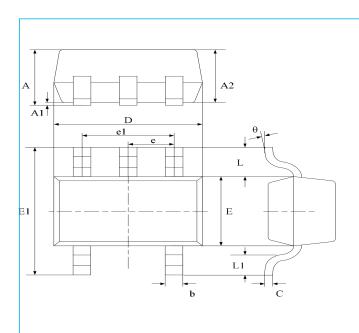

### SC70-5

| Symbol | Dimensions<br>In Millimeters |       | Dimensions<br>In Inches |        |  |

|--------|------------------------------|-------|-------------------------|--------|--|

|        | Min                          | Max   | Min                     | Max    |  |

| A      | 0.800                        | 1.100 | 0.035                   | 0.043  |  |

| A1     | 0.000                        | 0.100 | 0.000                   | 0.004  |  |

| A2     | 0.800                        | 0.900 | 0.035                   | 0.039  |  |

| b      | 0.150                        | 0.350 | 0.006                   | 0.014  |  |

| С      | 0.080                        | 0.150 | 0.003                   | 0.006  |  |

| D      | 1.8500                       | 2.150 | 0.079                   | 0.087  |  |

| Е      | 1.100                        | 1.400 | 0.045                   | 0.053  |  |

| E1     | 1.950                        | 2.200 | 0.085                   | 0.096  |  |

| e      | 0.850 typ.                   |       | 0.026 typ.              |        |  |

| e1     | 1.200                        | 1.400 | 0.047                   | 0.055  |  |

| L      | 0.42 ref.                    |       | 0.02                    | l ref. |  |

| L1     | 0.260                        | 0.460 | 0.010                   | 0.018  |  |

| θ      | 0°                           | 8°    | 0°                      | 8°     |  |

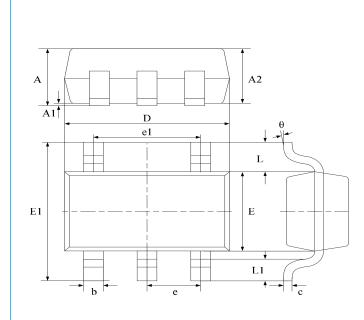

### SOT23-5

|        | Dimensions     |            | Dimensions |        |

|--------|----------------|------------|------------|--------|

| Symbol | In Millimeters |            | In Ir      | iches  |

|        | Min            | Max        | Min        | Max    |

| A      | 1.040          | 1.350      | 0.042      | 0.055  |

| A1     | 0.040          | 0.150      | 0.002      | 0.006  |

| A2     | 1.000          | 1.200      | 0.041      | 0.049  |

| b      | 0.380          | 0.480      | 0.015      | 0.020  |

| c      | 0.110          | 0.210      | 0.004      | 0.009  |

| D      | 2.720          | 3.120      | 0.111      | 0.127  |

| Е      | 1.400          | 1.800      | 0.057      | 0.073  |

| E1     | 2.600          | 3.000      | 0.106      | 0.122  |

| e      | 0.950          | 0 typ.     | 0.03       | 7 typ. |

| e1     |                | 1.900 typ. |            | 8 typ. |

| L      | 0.700 ref.     |            | 0.028 ref. |        |

| L1     | 0.300          | 0.600      | 0.012      | 0.024  |

| θ      | 0°             | 8°         | 0°         | 8°     |

# **Package Information**

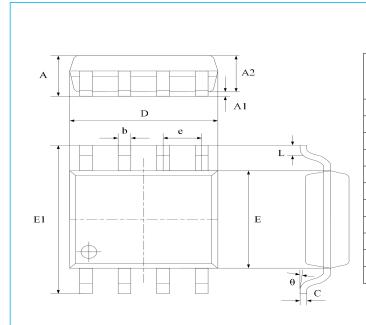

### SOP-8

| Symbol | Dimensions<br>In Millimeters |       | Dimensions<br>In Inches |        |

|--------|------------------------------|-------|-------------------------|--------|

|        | Min                          | Max   | Min                     | Max    |

| A      | 1.370                        | 1.670 | 0.056                   | 0.068  |

| Al     | 0.070                        | 0.170 | 0.003                   | 0.007  |

| A2     | 1.300                        | 1.500 | 0.053                   | 0.061  |

| b      | 0.306                        | 0.506 | 0.013                   | 0.021  |

| С      | 0.203 typ.                   |       | 0.008 typ.              |        |

| D      | 4.700                        | 5.100 | 0.192 0.208             |        |

| Е      | 3.820                        | 4.020 | 0.156                   | 0.164  |

| E1     | 5.800                        | 6.200 | 0.237                   | 0.253  |

| e      | 1.270 typ.                   |       | 0.05                    | 0 typ. |

| L      | 0.450                        | 0.750 | 0.018                   | 0.306  |

| θ      | 0°                           | 8°    | 0°                      | 8°     |

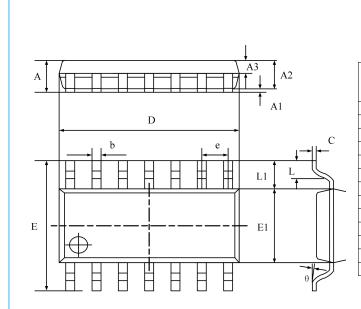

### SOP-14

|        | Dimensions     |       | Dimensions |           |  |

|--------|----------------|-------|------------|-----------|--|

| Symbol | In Millimeters |       | In Inches  |           |  |

| -      | Min            | Max   | Min        | Max       |  |

| A      | 1.450          | 1.850 | 0.059      | 0.076     |  |

| A1     | 0.100          | 0.300 | 0.004      | 0.012     |  |

| A2     | 1.350          | 1.550 | 0.055      | 0.063     |  |

| A3     | 0.550          | 0.750 | 0.022      | 0.031     |  |

| b      | 0.406typ.      |       | 0.017typ.  |           |  |

| С      | 0.20           | 3typ. | 0          | 0.008typ. |  |

| D      | 8.630          | 8.830 | 0.352      | 0.360     |  |

| E      | 5.840          | 6.240 | 0.238      | 0.255     |  |

| E1     | 3.850          | 4.050 | 0.157      | 0.165     |  |

| e      | 1.270 typ.     |       | 0.05       | 0 typ.    |  |

| L1     | 1.040 ref.     |       | 0.04       | 1 ref.    |  |

| L      | 0.350          | 0.750 | 0.014      | 0.031     |  |

| θ      | 2°             | 8°    | 2°         | 8°        |  |